RTC clock synchronization buffer driver delay chip

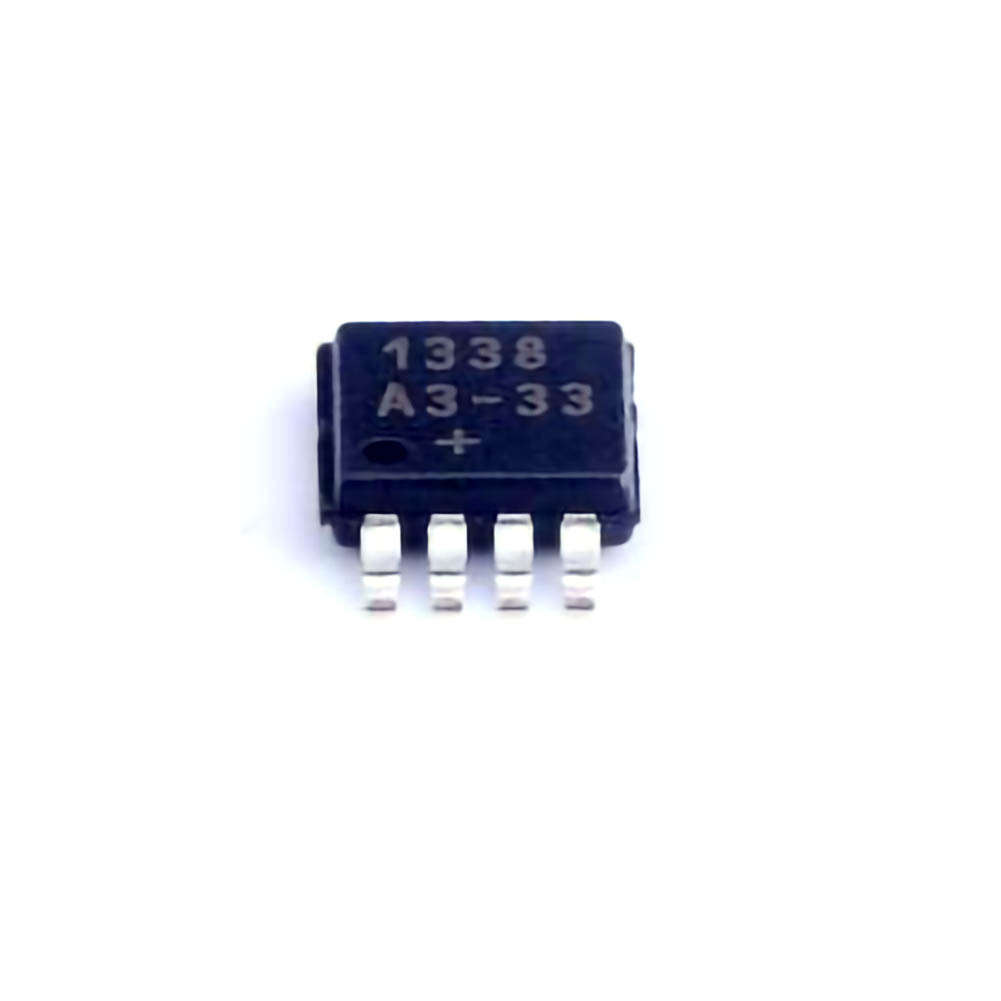

Hissə nömrəsi

RENESAS (Renesas)/IDT

İstehsalçılar

I2C interface (RTC), working voltage: 2.7V-5.5V

Təsvir

68578 PCS

Stokda

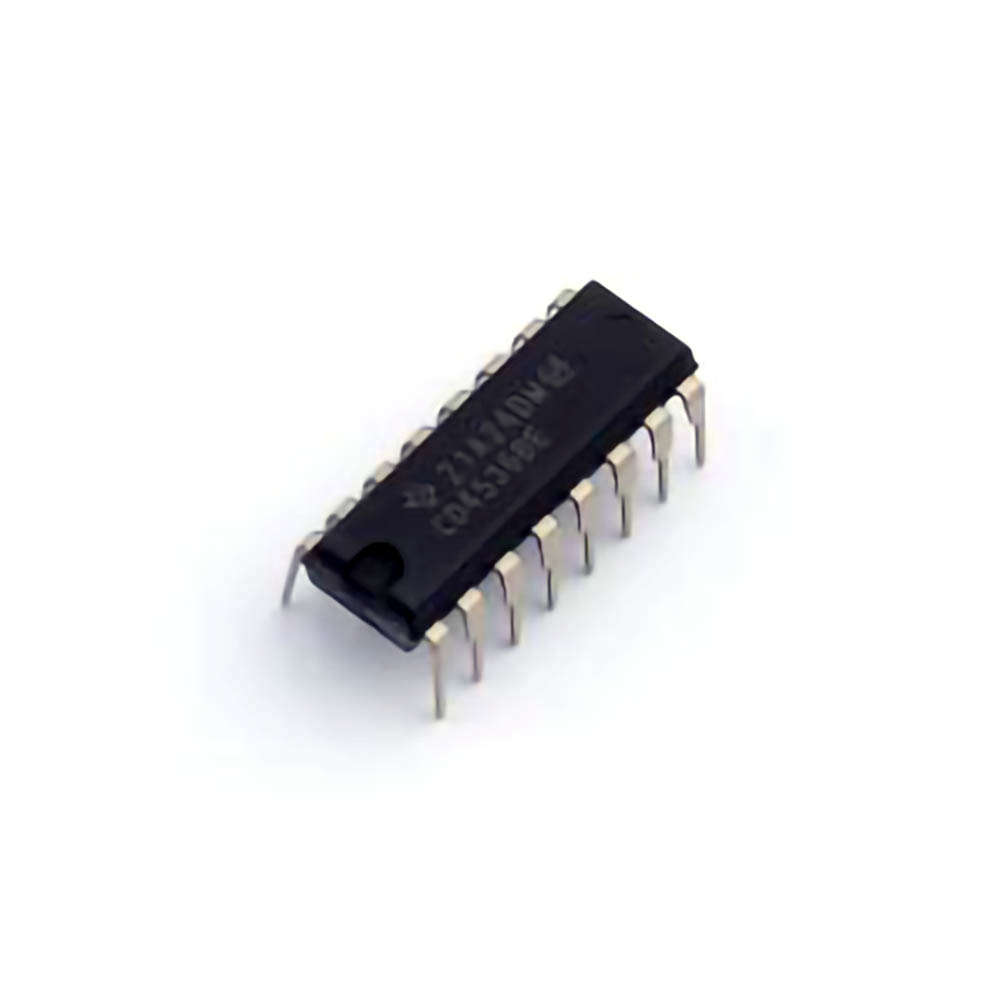

Hissə nömrəsi

TI (Texas Instruments)

İstehsalçılar

CMOS Programmable Timer 16-PDIP -55 to 125

Təsvir

72289 PCS

Stokda

Hissə nömrəsi

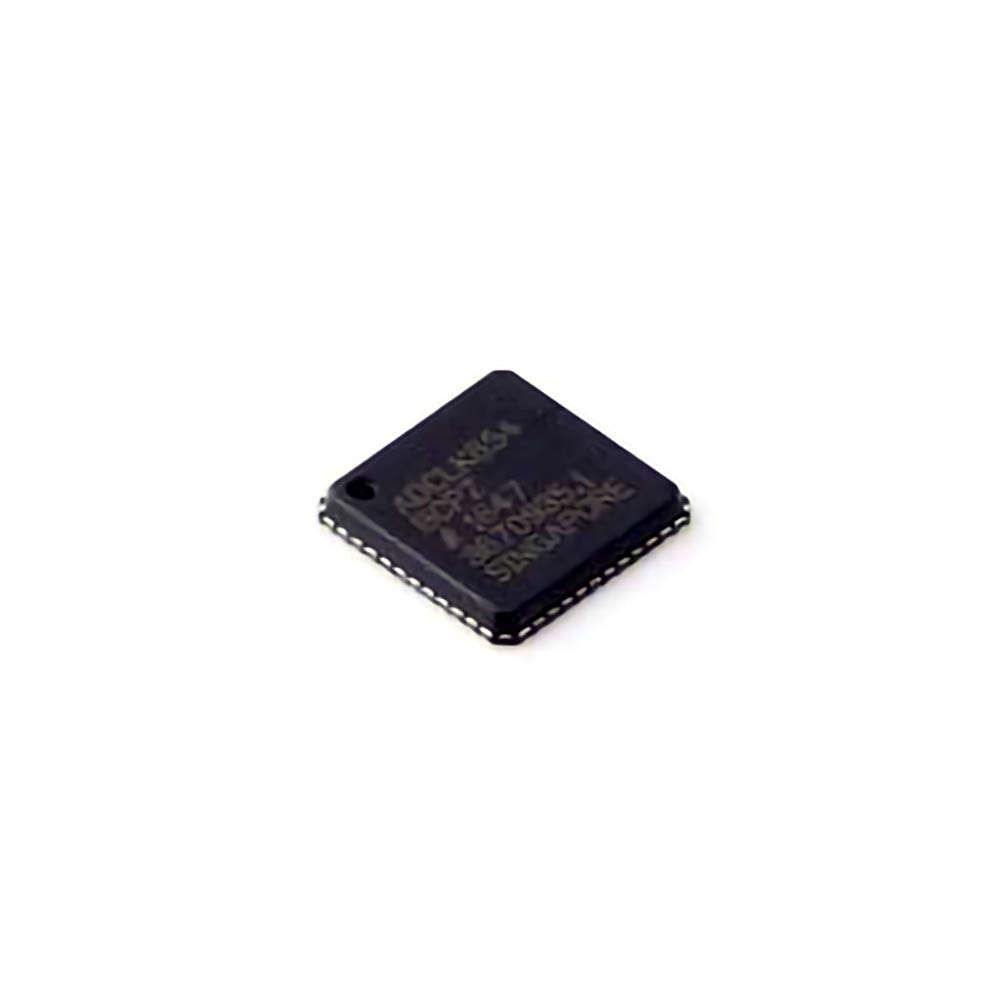

ADI (Adeno)/MAXIM (Maxim)

İstehsalçılar

I2C, 2-wire serial port

Təsvir

66681 PCS

Stokda

Hissə nömrəsi

onsemi (Ansemi)

İstehsalçılar

The NB100LVEP221 is a low-skew 2:1:20 differential driver for clock distribution, accepting two clock sources into one input multiplexer. The two clock inputs are differential ECL/PECL; CLK1/CLK1bar can also accept HSTL signal levels. The LVPECL input signal can be differential or single-ended (if using the VBB output). The LVEP221 specifically guarantees low output-to-output skew. Excellent design, layout, and handling techniques minimize skew within the device and from device to device. To ensure the tightest skew, both sides of the differential output are equally terminated to 50Ω, even if only one side is used. If an output pair is not used, both outputs can be left open (unterminated) without affecting the skew ratio. Like most other ECL devices, the NB100LVEP221 can be powered from a positive VCC supply in LVPECL mode. Therefore, using the LVEP221 in +3.3 V or +2.5 V systems enables high performance clock distribution. In a PECL environment, serial or Thevenin line terminations are often used because they do not require an additional power supply. Designers should refer to application note AND8020/D for more information on using PECL termination. Only the VBB pin, the internally generated supply voltage, is provided for this device. In the case of single-ended LVPECL inputs, tie the unused differential input to VBB as the switch reference voltage. VBB can also re-bias the AC-coupled input. When used, decouple VBB and VCC through a 0.01 uF capacitor and limit current to source or sink 0.5 mA. VBB should be left open when not in use. Single-ended CLK input operation is limited to VCC >= 3.0 V in LVPECL mode and VEE <= -3.0 V in NECL mode.

Təsvir

81651 PCS

Stokda

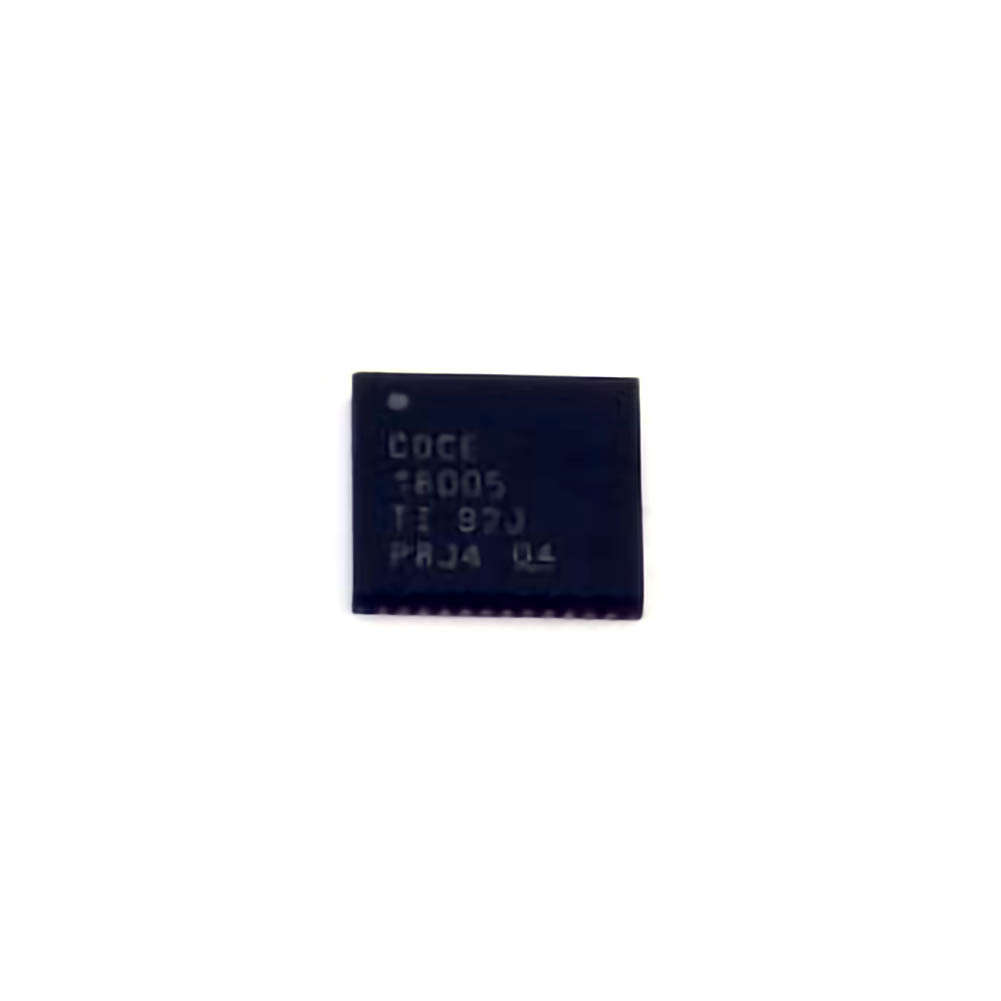

Hissə nömrəsi

TI (Texas Instruments)

İstehsalçılar

CDCM9102 Low Noise Dual Channel 100MHz PCIe Clock Generator

Təsvir

50126 PCS

Stokda

Hissə nömrəsi

HTCSEMI (Haitian core)

İstehsalçılar

Micro-power real-time clock with 56 Х 8 RAM serial interface, supports oscillator operation in battery mode

Təsvir

89244 PCS

Stokda

Hissə nömrəsi

Micro Crystal (Swiss Micro Crystal)

İstehsalçılar

Təsvir

58193 PCS

Stokda